# Vivienne Sze

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

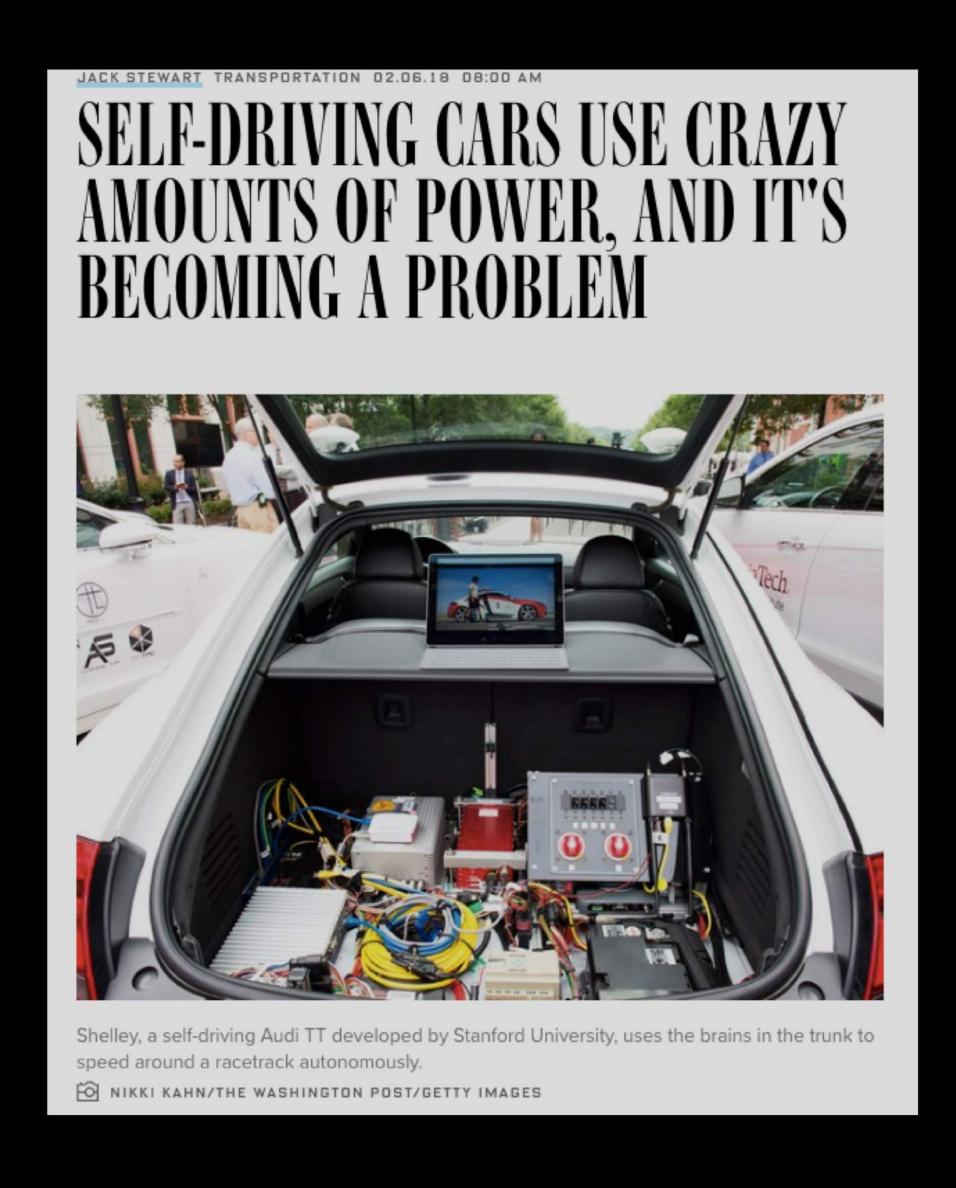

## Computing challenge for self-driving cars

Cameras and radar generate ~6 gigabytes of data every 30 seconds

Self-driving car prototypes use approximately 2,500 Watts of computing power

Generates wasted heat and some prototypes need water-cooling

SOURCE: WIRED, FEB 2018

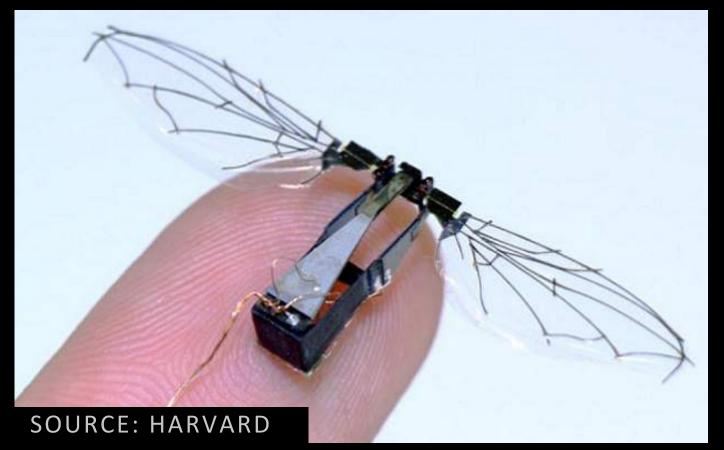

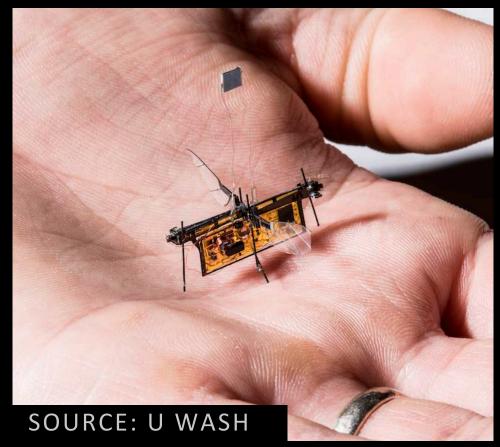

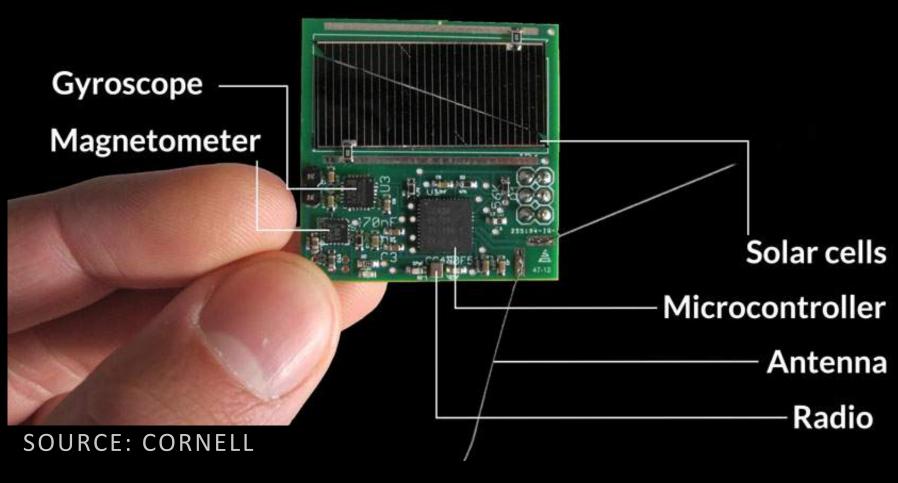

# Robots consuming < 1 Watt for actuation

#### Low energy robotics

- Miniature aerial vehicles

- Lighter than air vehicles

- Miniature satellites

- Micro unmanned gliders

SOURCE: MIT, HARVARD

# Existing processors consume too much power

< 1 Watt

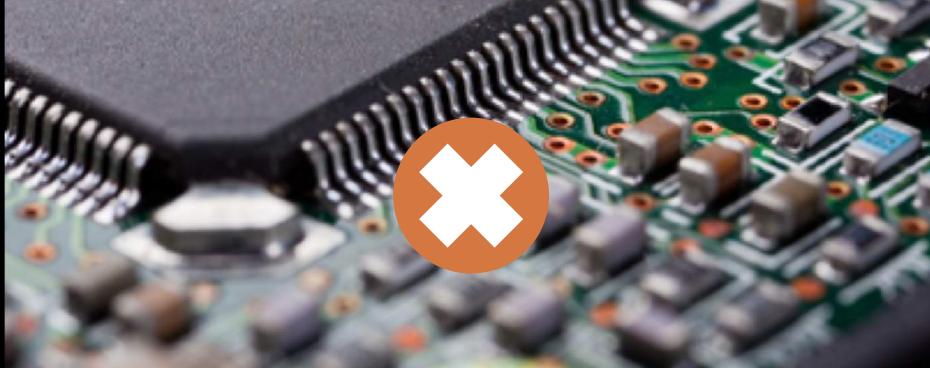

# Transistors are NOT getting more efficient

Slowdown of Moore's Law and Dennard Scaling General purpose microprocessors are not getting faster or more efficient

- Need specialized hardware for significant improvement in speed and energy efficiency

- Redesign computing hardware from the ground up!

SOURCE: INTEL, PRESS REPORTS, BOB COLWELL, LINLEY GROUP, IB CONSULTING, THE ECONOMIST

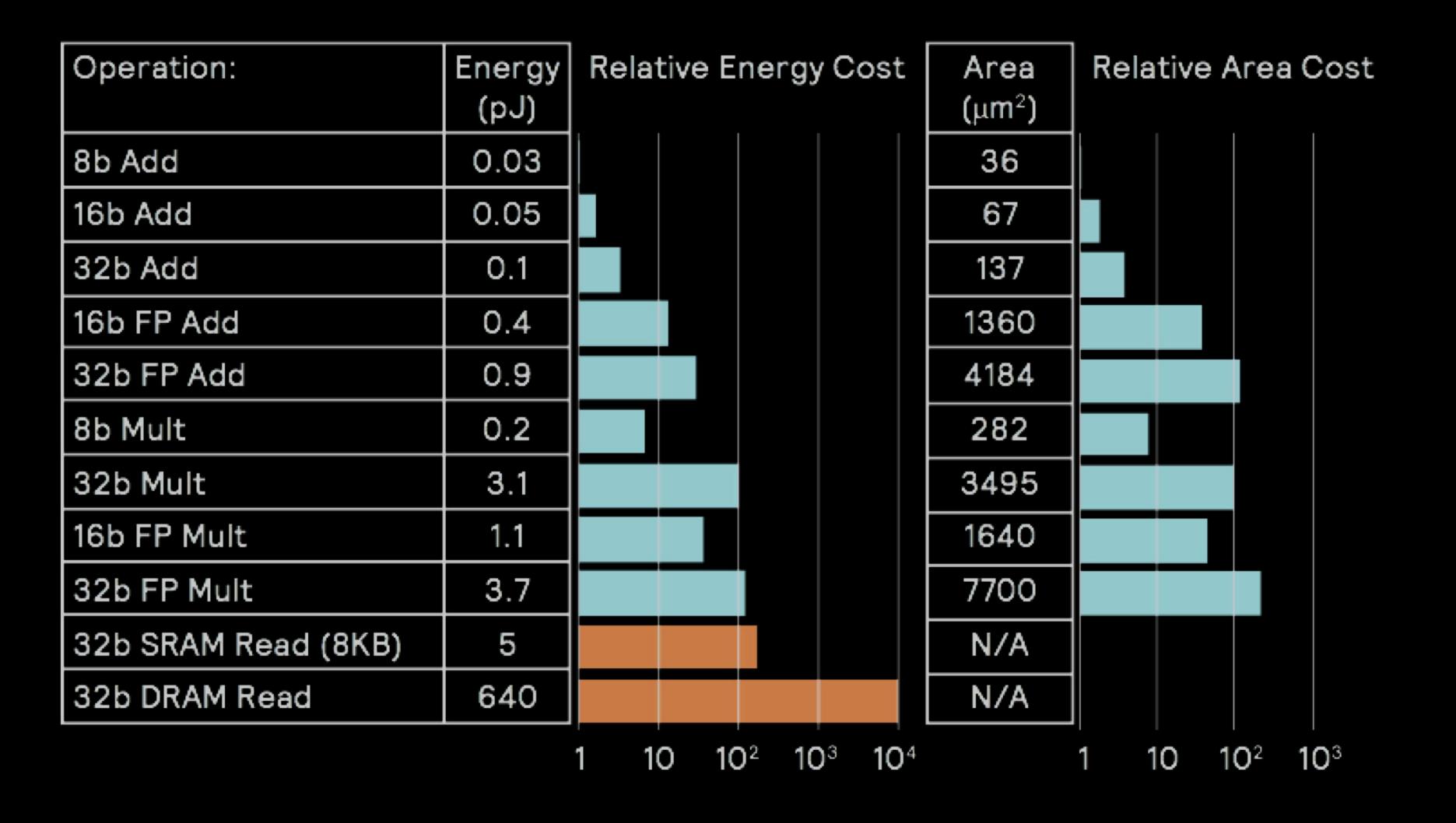

## Power dominated by data movement

Memory access is orders of magnitude higher energy than compute

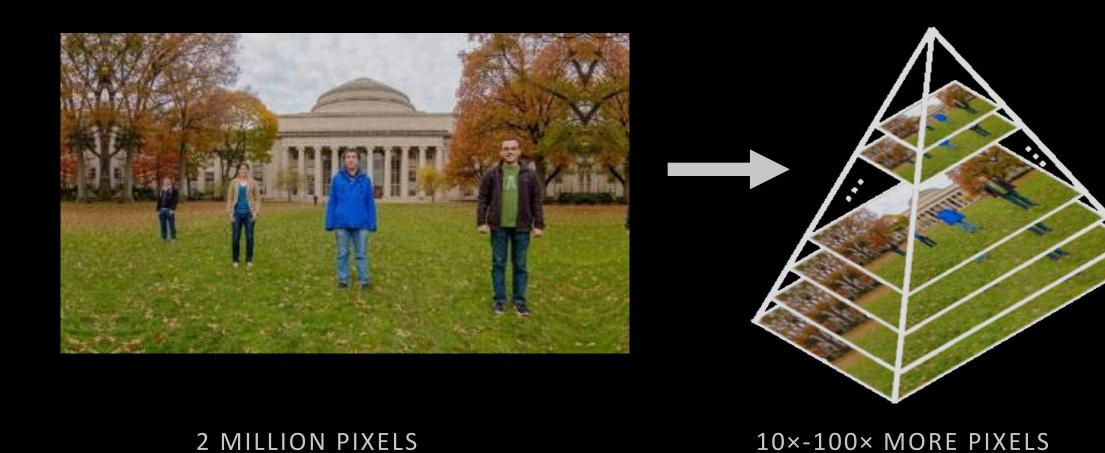

# Autonomous navigation uses a lot of data

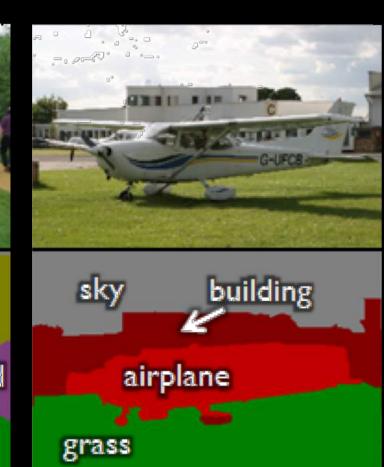

#### Semantic Understanding

- High frame rate

- Large resolutions

- Data expansion

#### Geometric Understanding

Growing map size

SOURCE: PIRE, RAS 2017

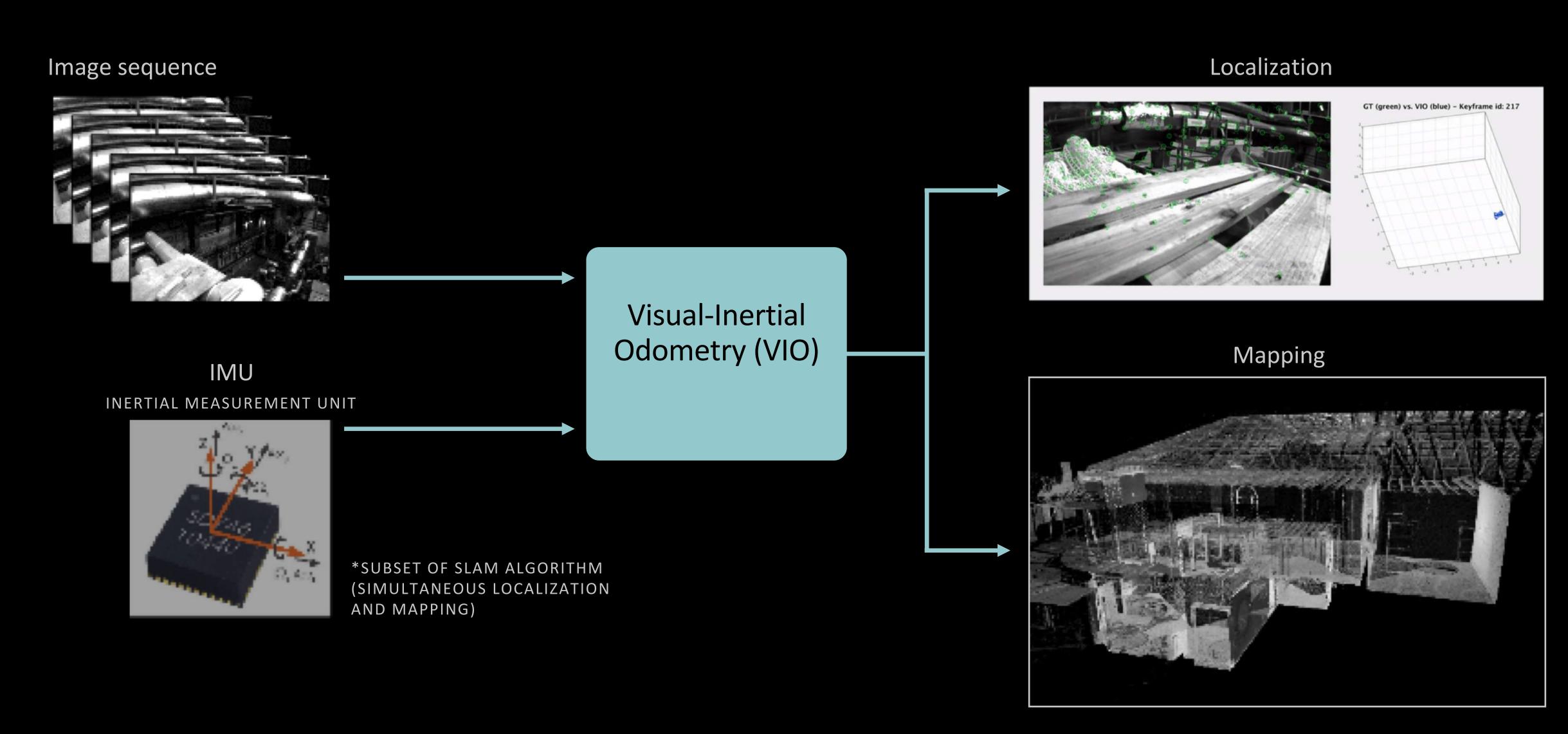

# Visual-inertial localization

# Determines location/orientation of robot from images and IMU

#### Localization at under 25 mW

# REPORT OF THE PROPERTY OF THE

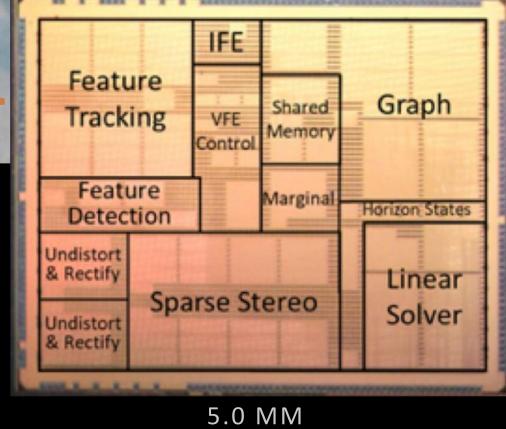

Navion

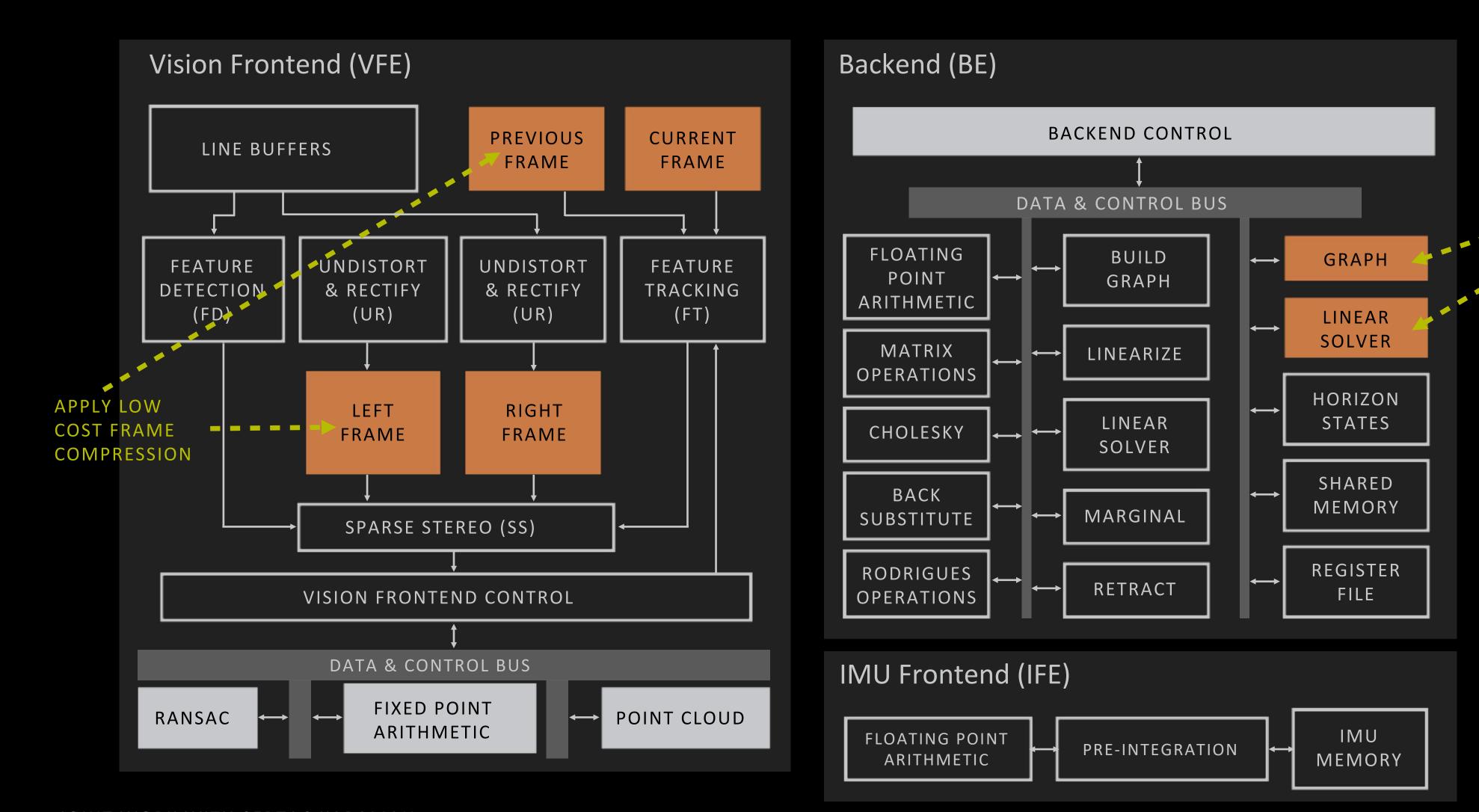

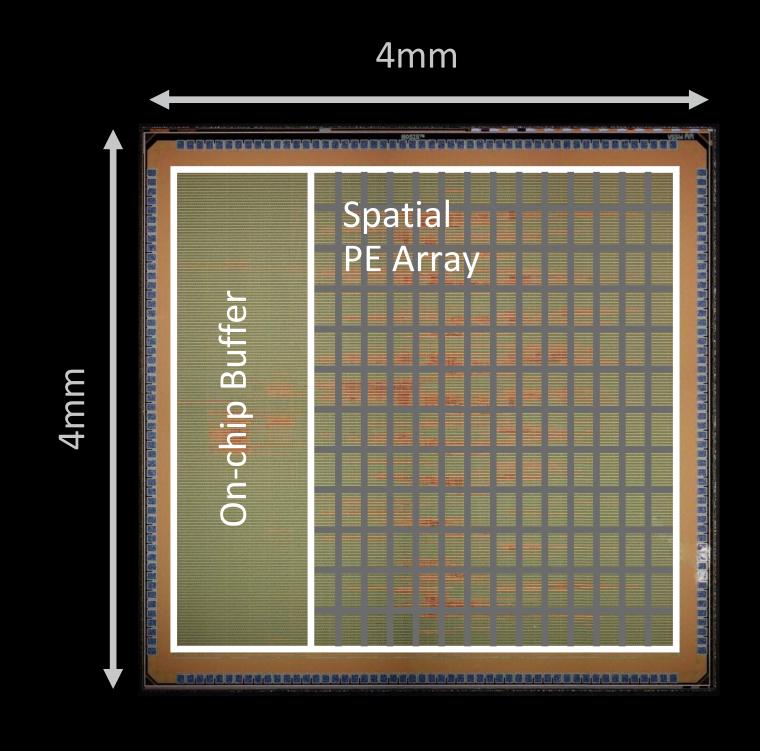

# First chip that performs complete Visual-Inertial Odometry

Front-End for Camera (Feature detection, tracking, and outlier elimination)

Front-End for IMU (Pre-integration of accelerometer and gyroscope data)

Technology

Back-End Optimization of Pose Graph

Consumes 684×

and 1582× less

energy than

mobile and

desktop CPUs,

respectively

1 V

Chip area (mm²)  $4.0 \times 5.0$  $752 \times 480$ 28 – 171 fps Core area (mm²)  $3.54 \times 4.54$ Camera Rate 16 – 90 fps Logic Gates Keyframe Rate 2,043 kgates SRAM 24 mW Average Power 854KB 10.5 - 59.1VFE Frequency GOPS 62.5 MHz BE Frequency 1 - 5.783.3 MHz GFLOPS

Supply

Resolution

65nm CMOS

SOURCE: ZHANG, RSS 2017; SULEIMAN, VLSI 2018

# Key methods to reduce data size

Navion: Fully integrated system — no off-chip processing or storage

Use compression and exploit sparsity to reduce memory down to 854kB

**EXPLOIT SPARSITY IN**

## Understanding the environment

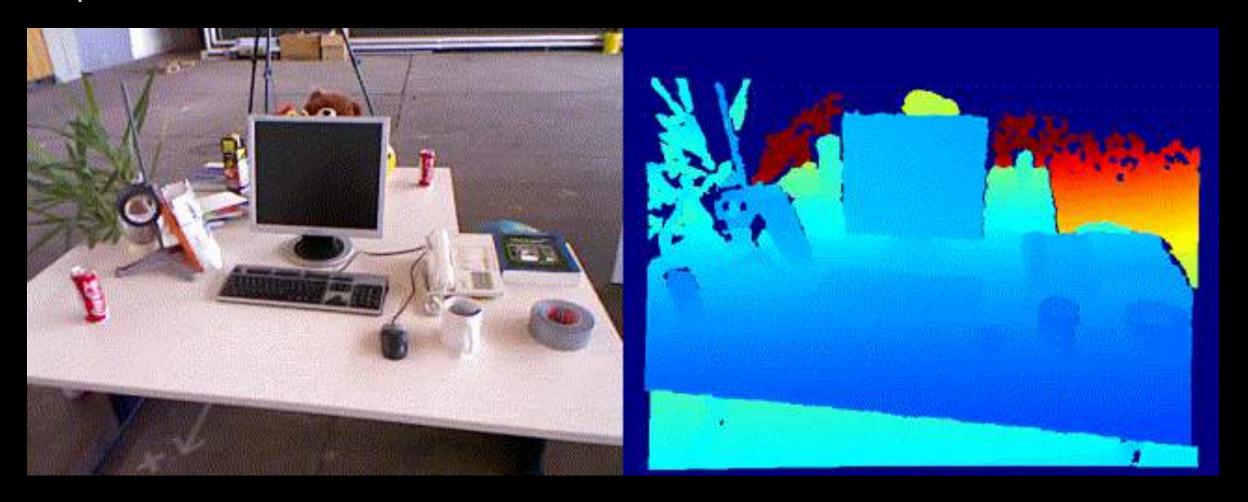

#### **Depth Estimation**

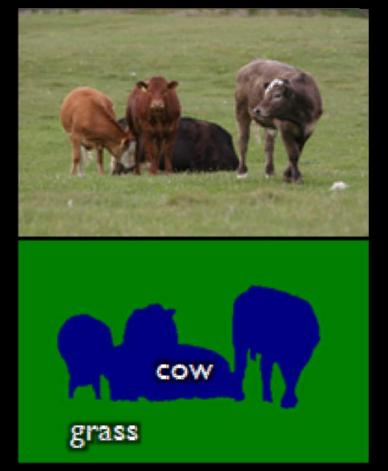

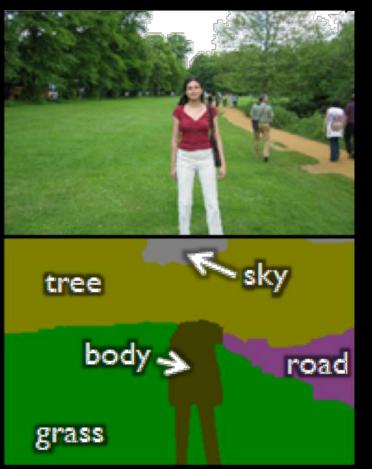

#### Semantic Segmentation

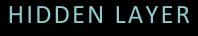

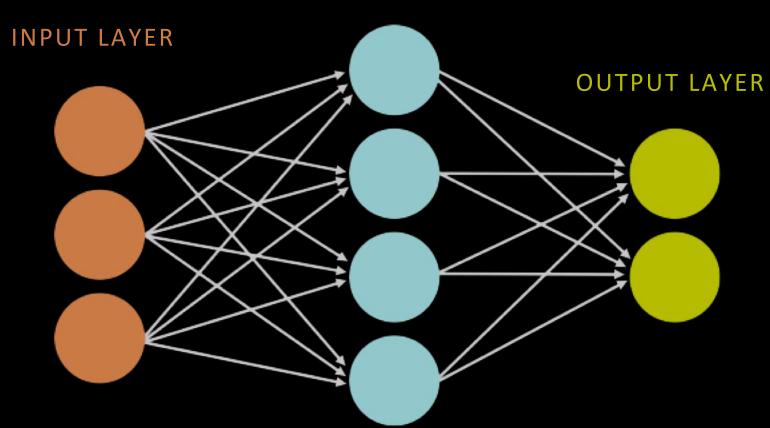

State-of-the-art approaches use Deep Neural Networks which require up to several hundred millions of operations and weights to compute!

> 100× more complex than video compression

## Properties we can leverage

# Operations exhibit high parallelism → high throughput possible

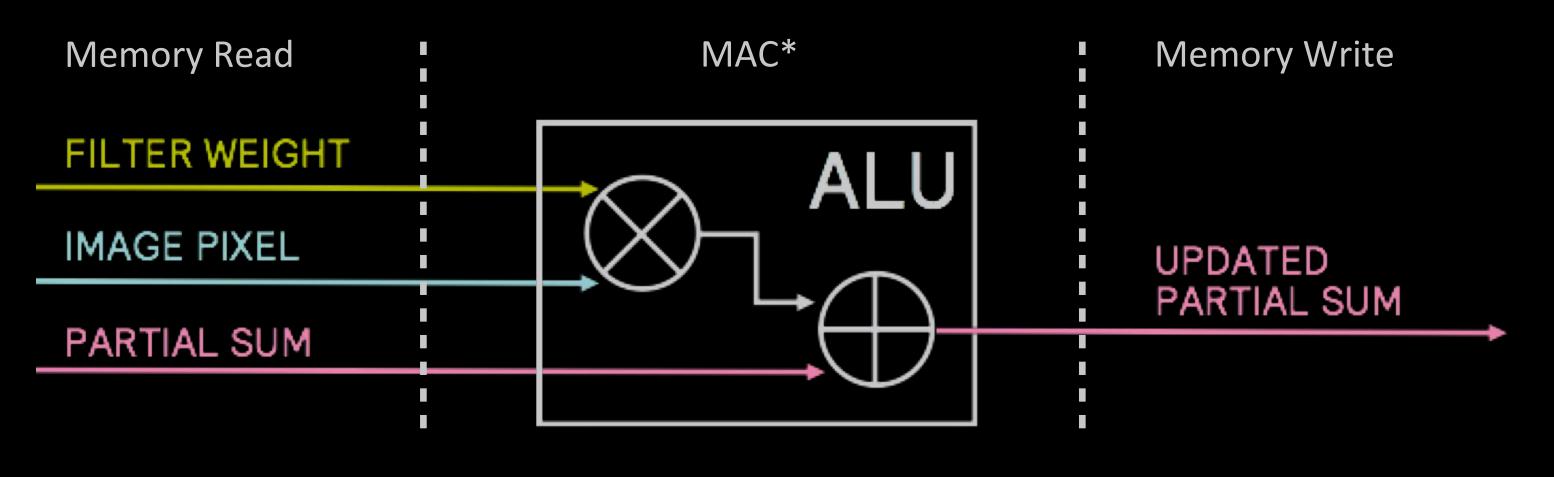

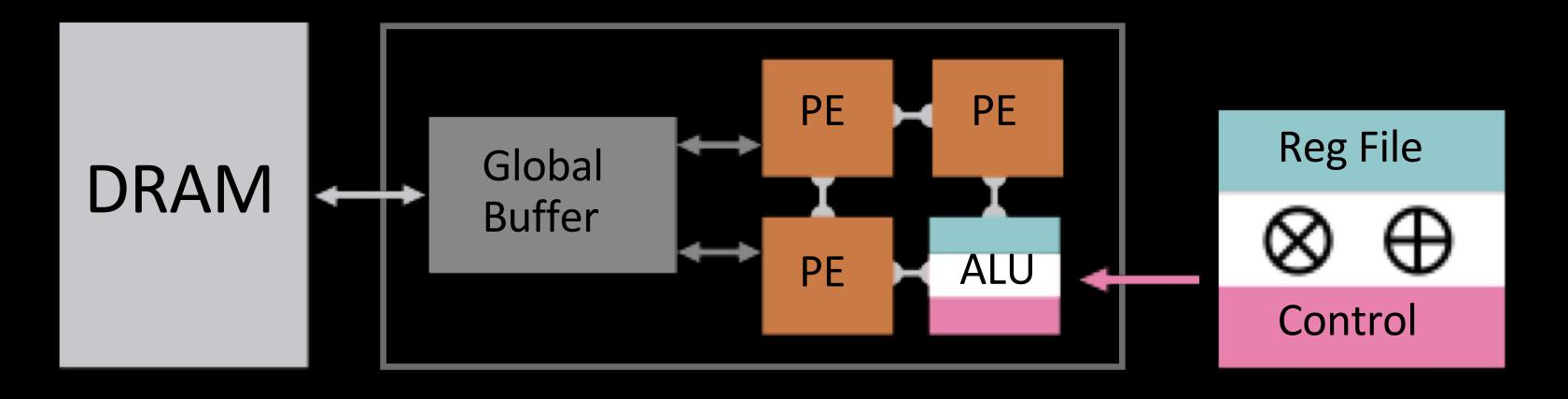

#### Memory Access is the Bottleneck

\*MULTIPLY-AND-ACCUMULATE

Worst Case: all memory R/W are DRAM accesses

Example: AlexNet has 724M MACs

→ 2896M DRAM accesses required

## Properties we can leverage

#### Operations exhibit high parallelism

→ high throughput possible

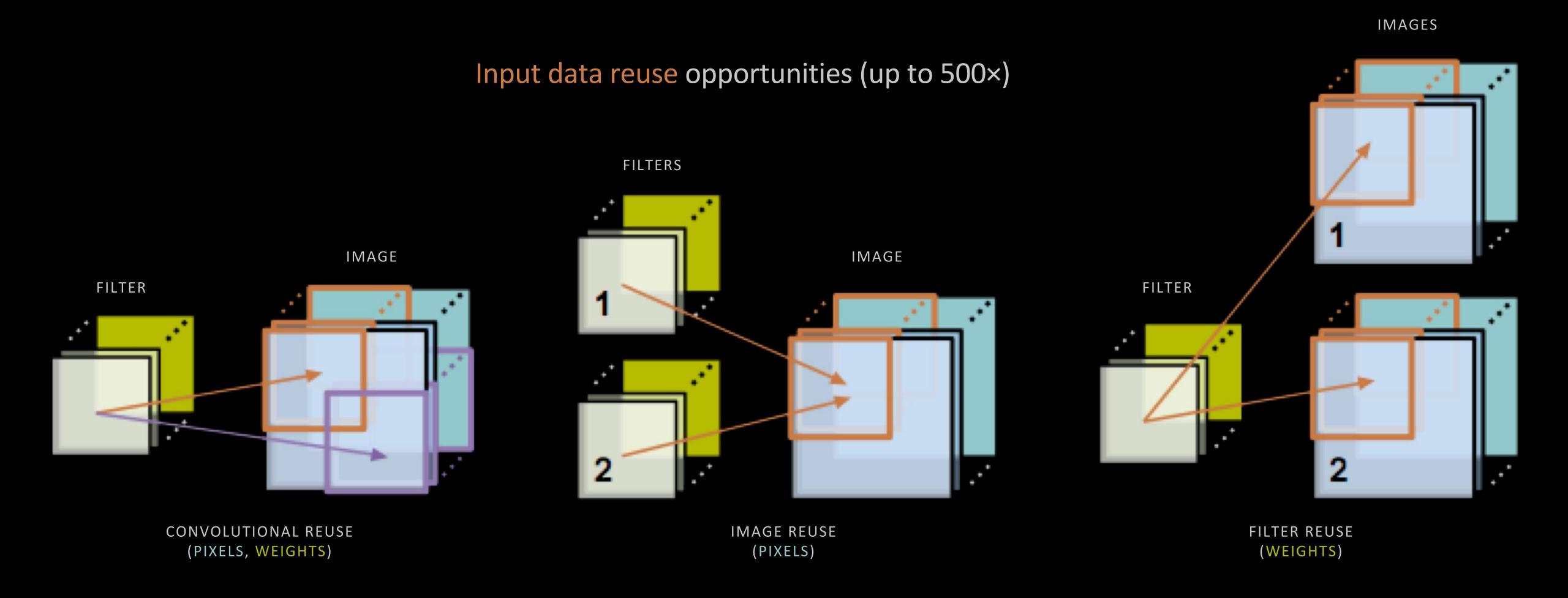

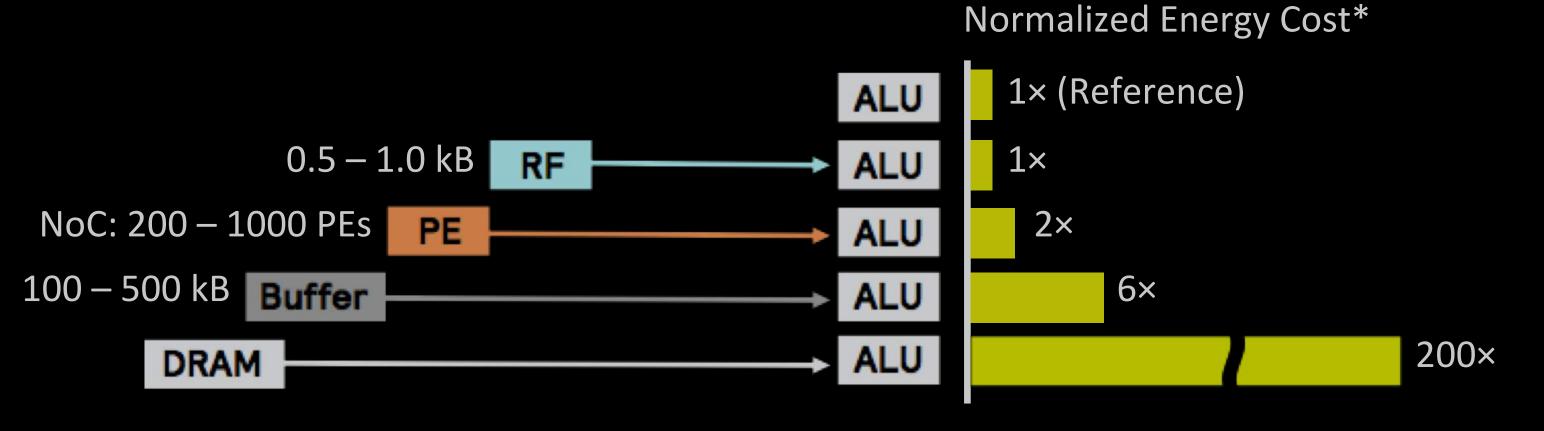

## Exploit data reuse at low-cost memories

Specialized hardware with small (< 1kB) low cost memory near compute

Farther and larger memories consume more power

\*MEASURED FROM A COMMERCIAL 65nm PROCESS

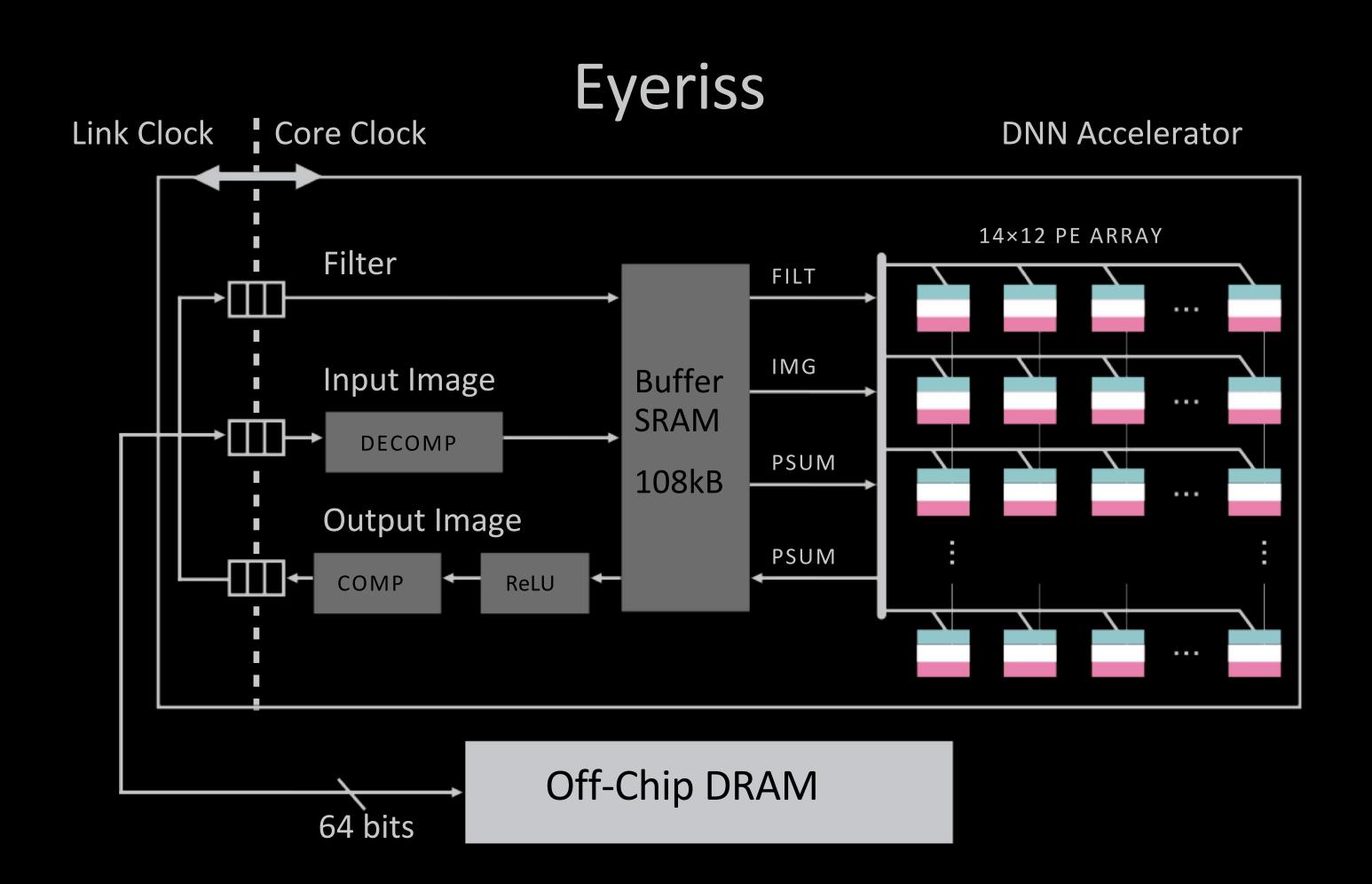

# Deep neural networks at under 0.3 W

Exploits data reuse for 100× reduction in memory accesses from global buffer and 1400× reduction in memory accesses from off-chip DRAM

Overall > 10× energy reduction compared to a mobile GPU

JOINT WORK WITH JOEL EMER SOURCE: CHEN, ISSCC 2016

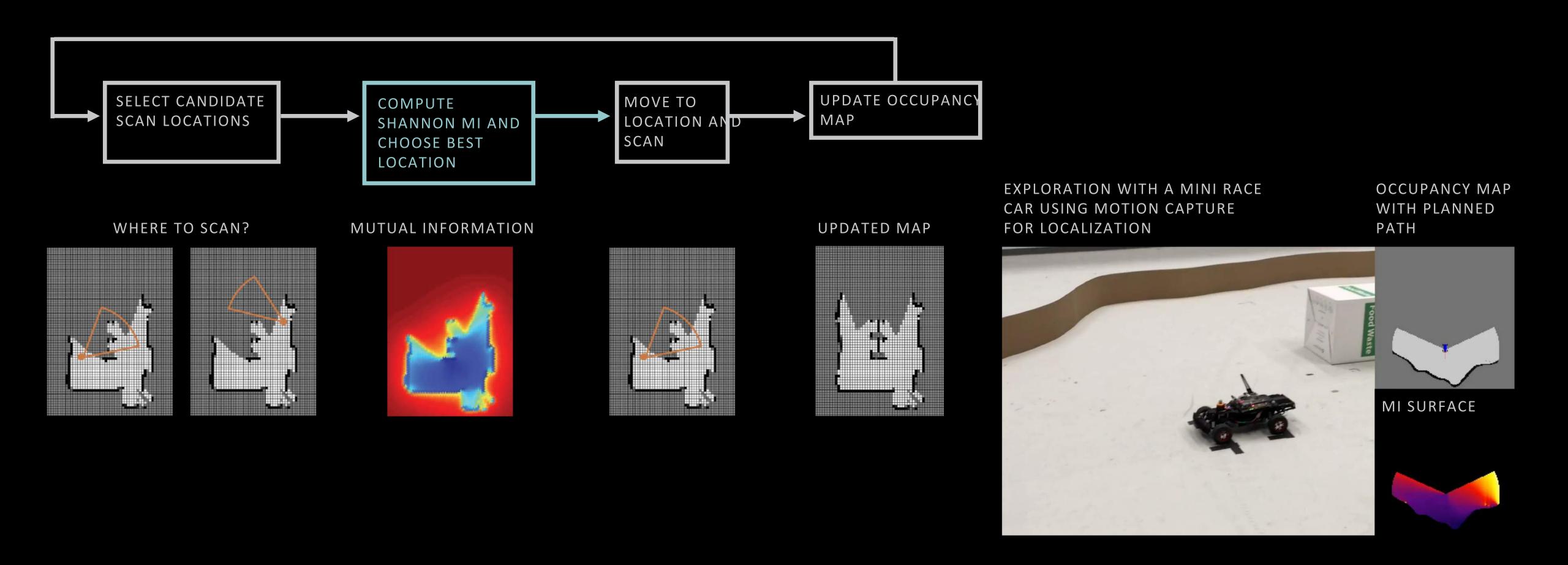

# Where to go next: planning and mapping

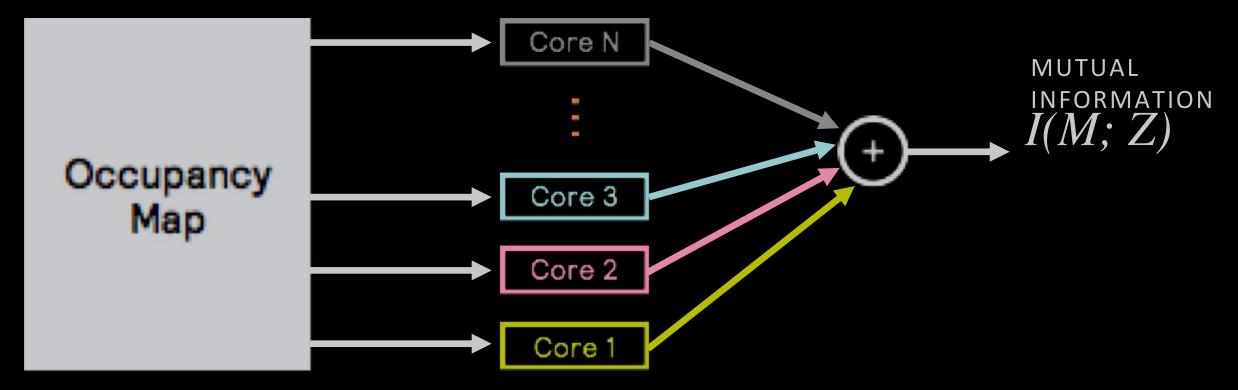

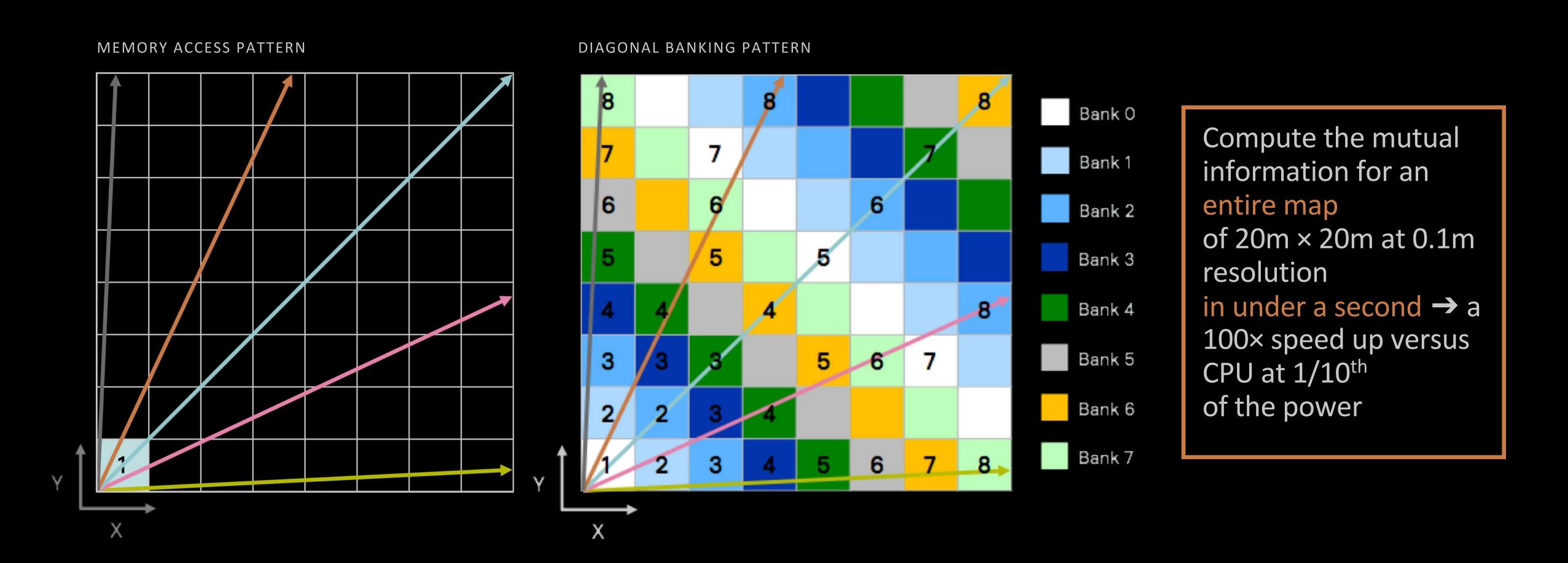

Robot Exploration: decide where to go by computing Shannon Mutual Information

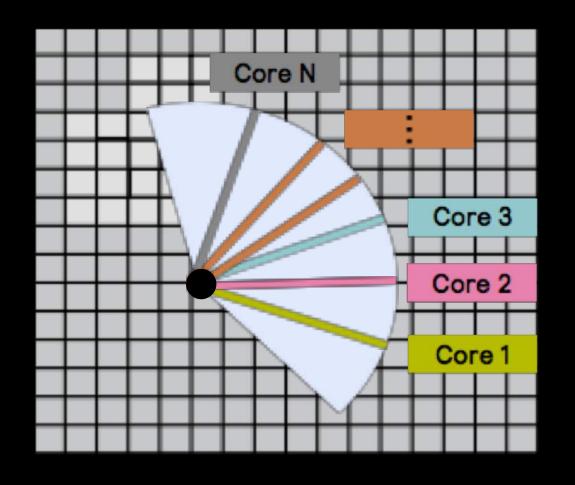

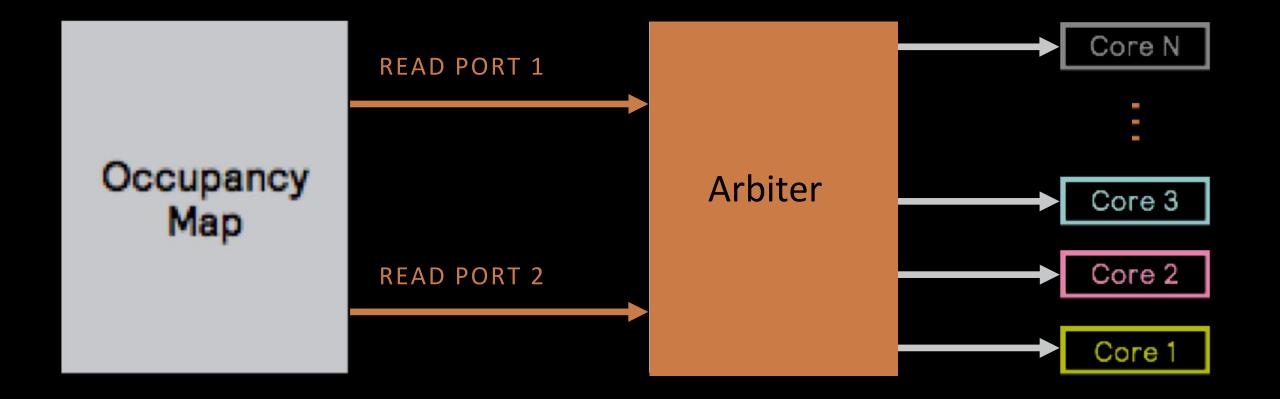

# Challenge is data delivery to all cores

#### Process multiple beams in parallel

#### Data delivery from memory is limited

# Specialized memory architecture

Break up map into separate memory banks and use a novel storage pattern to minimize read conflicts when processing different beams in parallel

### Summary

Efficient computing is critical for advancing the progress of autonomous robots, particularly at the smaller scales → Critical step to making autonomy ubiquitous!

In order to meet computing demands in terms of power and speed, need to redesign computing hardware from the ground up

Focus on data movement!

Specialized hardware opens up new opportunities for the codesign of algorithms and hardware → Innovation opportunities for the future of robotics!